- 首页

- 新闻

- 产品

-

解决方案

- 解决方案

- 导航终端生产线质检系统方案

- 预备应急通信系统方案

- 技术与研发

- 关于我们

产品简介

设计服务

产品简介

设计服务

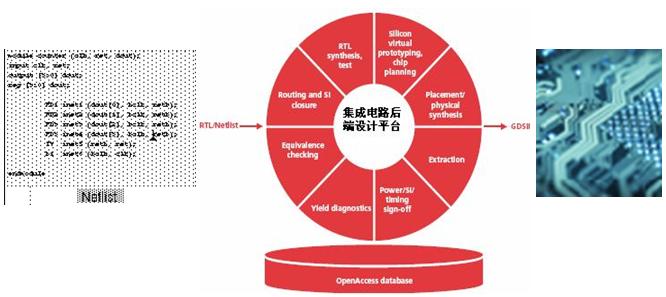

“中心”所属实验室在超深亚微米,超大规模片集成电路设计后端设计方法学的以下方向上进行深入研究:(1)超深亚微米(90nm、65nm、45nm)芯片的后端低功耗设计。(2)统计学角度的静态时序分析(SSTA)。(3)占空比对称的时钟树的算法与结构的优化。(4)后端设计流程的整体自动化。

从RTL到GDSII的集成电路后端设计流程